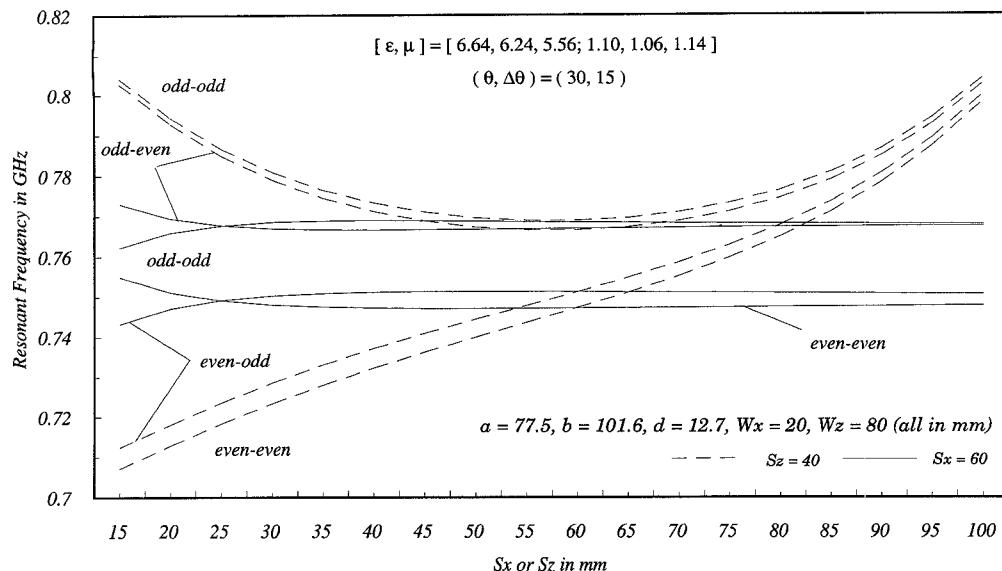

Fig. 4.  $f_r$  of all modes of a patch resonator as a function of  $s_z$  (solid lines) and  $s_x$  (broken lines).

even and even-odd modes. Also in this region, they exhibit totally contrasting behavior—namely,  $f_r$ 's of  $o-e$  and  $o-o$  modes decrease, while those of  $e-e$  and  $e-o$  steadily increase. As the transverse separation between the patches increases, resonant frequencies of the array are significantly influenced by the sidewalls of the waveguide. They all tend to increase towards the same value.

## V. CONCLUSION

Resonant properties of a four microstrip patch resonator array, printed on an anisotropic substrate, were analyzed. Good agreement with limited published data was found, and ample numerical results for resonant frequencies of the resonator array were presented as functions on the geometrical and substrate material parameters.

## REFERENCES

- [1] N. G. Alexopoulos, "Integrated structures on anisotropic substrates," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-33, no. 10, pp. 847-881, Oct. 1985.

- [2] D. M. Pozar, "Radiation and scattering from a microstrip patch on uniaxial substrate," *IEEE Trans. Antenna. Propagat.*, vol. AP-35, no. 6, pp. 613-621, June 1987.

- [3] T. Q. Ho, B. Beker, Y. C. Shih and Y. Chen, "Microstrip resonators on anisotropic substrates," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-40, no. 4, pp. 762-765, Apr. 1992.

- [4] D. W. Berreman, "Optics in stratified and anisotropic media:  $4 \times 4$  matrix formulation," *J. Opt. Soc. Am.*, vol. 62, no. 4, pp. 502-510, Apr. 1972.

- [5] C. M. Krowne, "Fourier transformed matrix method of finding propagation characteristics of layered anisotropic media," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-32, no. 12, pp. 1617-1625, Dec. 1984.

- [6] C. R. Paiva and A. M. Barbosa, "Spectral representation of self-adjoint problems for layered anisotropic waveguides," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-39, no. 2, pp. 330-338, Feb. 1991.

- [7] Y. Chen and B. Beker, "Analysis of single and coupled microstrip lines on anisotropic substrates using differential matrix operators and the spectral-domain method," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-41, no. 1, pp. 123-128, Jan. 1993.

- [8] —, "Dispersion characteristics of open and shielded microstrip lines under a combined principal axes rotation of electrically and magnetically

anisotropic substrates," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-41, no. 4, pp. 673-679, Apr. 1993.

- [9] T. Itoh, "Analysis of microstrip resonators," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-22, no. 11, pp. 946-952, Nov. 1974.

- [10] T. Itoh and W. Menzel, "A full-wave analysis method for open microstrip structures," *IEEE Trans. Antenna. Propagat.*, vol. AP-29, pp. 63-68, 1981.

## A Technique for Minimizing Intermodulation Distortion of GaAs FET's

Haruhiko Koizumi, Shunsuke Nagata and Kunihiko Kanazawa

**Abstract**—This paper describes the theory to minimize the intermodulation distortion under certain current bias condition for GaAs FET's. A device-parametric study has been done to obtain the general equation that provides the lowest distortion condition as a function of an operating current. Based on the present theory, FET parameters have been designed practically.

## I. INTRODUCTION

In recent years, the microwave GaAs MESFET has been widely used for a variety of mobile communication systems. In those portable systems, what is most important is to reduce the operating current since the battery running time is a major concern. In addition, recent digital communication systems require the minimization of an intermodulation (IM) distortion in order to improve the error rate. However, it is difficult that GaAs FET's provide the low current and the low distortion characteristic at the same time. Therefore, the goal

Manuscript received February 1, 1994; revised May 31, 1994.

The authors are with the Electronic Research Laboratory, Matsushita Electronics Corporation, Osaka, Japan 569.

IEEE Log Number 9407308.

to design such devices is to determine the device parameter that gives the best IM characteristics under allowed current condition.

Many researchers have attempted to describe the distortion characteristics of GaAs FET's by using the harmonic balance technique with new models of nonlinearities in GaAs FET's or by analyzing nonlinear distortion in GaAs FET's [1]–[5]. Generally, the lowest IM distortion is discussed as a parameter of the operating current for a particular FET. However, the general relation between the operating current and the IM distortion as parameters of the gate bias and gate width has not been clarified. To design the optimum device is to determine these parameters at the same time. In this work, we show the general equation providing the relation between the lowest IM distortion and the operating current as a function of the gate bias and the gate width for the FET amplifier. Based on this general equation, we can design the gate width that offers the lowest IM distortion under the target current condition. It is noted that this theory provides the essential optimum condition. Therefore, this general equation about the IM distortion becomes a practical technique for circuit design. In this paper, this new technique is experimentally applied to the design of a GaAs FET amplifier.

## II. GENERAL EXPRESSION OF THE IM DISTORTION

In this section, the general equation that provides the lowest IM distortion under the allowed operating current is obtained. First, the output power and the IM distortion characteristic of the FET are described as a function of the gate width. Then, this distortion characteristic is defined as a parameter of the gate bias. Finally, the condition that provides the best IM distortion at the allowed operating current is obtained.

The output power for the FET with the unit gate width  $W_g$  is defined as  $P_{\text{OUT}}$ . Then, the total output power  $P_{\text{OUT}_n}$  for the FET that has an  $n$ -times as large as the unit gate width ( $W_{gn} = n * W_g$ ), is obtained as follows,

$$\begin{aligned} P_{\text{OUT}_n} &= n \cdot \text{Ga} \cdot \frac{P_{\text{IN}}}{n} \\ &= n \cdot \frac{P_{\text{OUT}}}{n} \\ &= P_{\text{OUT}}, \end{aligned} \quad (1)$$

where  $\text{Ga}$  and  $P_{\text{IN}}$  are the small-signal power gain and the input power of the unit gate width FET, respectively. As the input power is constant, the power injected to each unit gate width FET is divided by  $n$ . As a result,  $P_{\text{OUT}_n}$  is equal to  $P_{\text{OUT}}$ . In (1), we assume that FET's are small enough so distributed phase effects due to multiple gates can be ignored. Therefore,  $\text{Ga}$  is not a function of the gate width, and the gate width factor,  $n$ , is only for paralleling multiple gates.

On the other hand, as the third-order intermodulation distortion ( $\text{IM}_3$ ) is proportional to  $P_{\text{IN}}^3$ , the  $\text{IM}_3$  for the FET with the gate width  $W_{gn}$ ,  $\text{IM}_{3n}$ , is

$$\begin{aligned} \text{IM}_{3n} &= n \cdot \frac{\text{IM}_3}{n^3} \\ &= \frac{\text{IM}_3}{n^2}, \end{aligned}$$

or

$$\text{IM}_{3n} [\text{dB}] = \text{IM}_3 [\text{dB}] - 20 \cdot \log n. \quad (2)$$

When the gate width of the FET increases  $n$ -times, the  $\text{IM}_3$  increases only  $1/n^2$  in comparison with one of the unit gate width FET.

In general, the third-order intercept point ( $\text{IP}_3$ ) is used in normalizing the distortion performance of devices for comparison. It is defined as the output power at which the intermodulation distortion component equals the fundamental frequency output, when both are

extrapolated linearly (on log scales) from low signal levels. Then the  $\text{IP}_3$  of the FET with unit gate width is given by

$$\text{IP}_3 [\text{dB}] = P_{\text{OUT}} [\text{dB}] + \frac{P_{\text{OUT}} [\text{dB}] - \text{IM}_3 [\text{dB}]}{2}. \quad (3)$$

Using (1)–(3), the  $\text{IP}_3$  of the total FET with the gate width  $W_{gn}$ ,  $\text{IP}_{3n}$ , is obtained as follows,

$$\begin{aligned} \text{IP}_{3n} [\text{dB}] &= P_{\text{OUT}} [\text{dB}] + \frac{P_{\text{OUT}} [\text{dB}] - (\text{IM}_3 [\text{dB}] - 20 \cdot \log n)}{2} \\ &= \text{IP}_3 [\text{dB}] + 10 \cdot \log n. \end{aligned} \quad (4)$$

or

$$\text{IP}_{3n} = n \cdot \text{IP}_3. \quad (5)$$

Also, the  $\text{IP}_3$  is changed by the operating current. Then, we lead the equation by which the maximum  $\text{IP}_3$  is obtained to describe  $\text{IP}_3$  as a function of the operating current. For the unit gate width FET, the  $\text{IP}_3$  is defined as

$$\text{IP}_3 = f(i_{\text{ds}}), \quad (6)$$

where  $i_{\text{ds}}$  is the operating current of the unit gate width FET. In this case,  $i_{\text{ds}}$  is changed by the gate bias voltage  $V_{gs}$ . Therefore, the symbol of “ $i_{\text{ds}}$ ” means the gate bias condition. Combining (6) with (5), the  $\text{IP}_3$  of the FET with the gate width  $W_{gn}$ ,  $\text{IP}_{3n}$ , is

$$\text{IP}_{3n} = n \cdot f(i_{\text{ds}}). \quad (7)$$

Now, when the operating current of the FET with the gate width  $W_{gn}$  is defined as  $I_{\text{ds}}$ ,  $I_{\text{ds}}$  is given as follows by using  $i_{\text{ds}}$ ,

$$I_{\text{ds}} = n \cdot i_{\text{ds}}. \quad (8)$$

Therefore, from (7) and (8), the relation of the  $\text{IP}_3$  and the operating current of the FET with the gate width  $W_{gn}$  is

$$\text{IP}_{3n} = n \cdot f\left(\frac{I_{\text{ds}}}{n}\right). \quad (9)$$

Equation (9) means that  $\text{IP}_3$  is changed by two parameters, such as the gate width parameter  $n$  and operating current parameter  $I_{\text{ds}}$ . When the one of these parameters is fixed, the other parameter that maximizes the  $\text{IP}_3$  can be designed. In this case, the operating current is fixed. Therefore, this maximum  $\text{IP}_3$  condition is described as

$$\frac{\partial}{\partial n} \text{IP}_{3n} \Big|_{I_{\text{ds}}=\text{const}} = 0. \quad (10)$$

Substituting (9) to (10), the condition can be described as follows,

$$\begin{aligned} \frac{\partial}{\partial n} \text{IP}_{3n} &= \frac{\partial i_{\text{ds}}}{\partial n} \cdot \frac{\partial}{\partial i_{\text{ds}}} \text{IP}_{3n} \\ &= -\frac{I_{\text{ds}}}{n^2} \left[ \left( -\frac{I_{\text{ds}}}{i_{\text{ds}}^2} \right) f(i_{\text{ds}}) + \frac{I_{\text{ds}}}{i_{\text{ds}}} \frac{\partial}{\partial i_{\text{ds}}} f(i_{\text{ds}}) \right] \\ &= 0. \end{aligned}$$

Therefore,

$$f(i_{\text{ds}}) = i_{\text{ds}} \frac{\partial}{\partial i_{\text{ds}}} f(i_{\text{ds}}). \quad (11)$$

The solution of (11) corresponds to the point of tangency of the functional curve  $f(i_{\text{ds}})$  and a straight line passing through the origin  $(0, 0)$ . From (11), the condition of the maximum  $\text{IP}_3$  under the allowed operating current is provided. This result shows that the bias condition providing the maximum  $\text{IP}_3$  is constant for various gate width FET's. It is noted that for the target operating current, the optimum gate width offering the maximum  $\text{IP}_3$  can be designed by

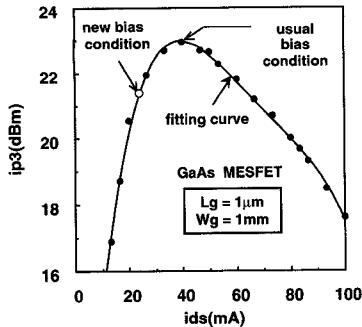

Fig. 1. Measurement result of the function  $f(i_{ds})$ .

(11). When the solution of this equation is represented as  $i_{ds0}$ , the optimum gate width  $W_{g0}$  is given as

$$W_{g0} = \frac{I_{ds}}{i_{ds0}} \cdot W_{g0}. \quad (12)$$

Therefore, the general expression of the maximum  $IP_3$  condition is represented as

$$IP_{3max} = \frac{I_{ds}}{i_{ds0}} \cdot f(i_{ds0}). \quad (13)$$

In this way, to achieve the maximum  $IP_3$  under the allowed operating current, the gate width and the gate bias condition are designed at the same time. The general expression of the IM distortion is represented by (11)–(13). From this theory, we can find that the usual design technique that separately decides the gate width and the gate bias cannot reach the maximum  $IP_3$ . It is noted that we can design the condition of the maximum  $IP_3$  for the target operating current, only when the gate width is provided by this general expression.

### III. DESCRIPTION OF THE FUNCTION $f(i_{ds})$

In the previous section, it is found that the function  $f(i_{ds})$  is required to calculate the condition that maximizes the  $IP_3$  for the allowed operating current. This function means the distortion characteristic of the unit gate width FET as a function of the gate bias condition. It is the objective of this section to describe the function  $f(i_{ds})$ . For example, we use the measurement result.

Figure 1 shows the measurement result of the relation between  $i_{ds}$  and  $IP_3$  for the unit gate width FET. The device used in the experiment is a 1- $\mu$ m gate-length and -2 V threshold voltage GaAs MESFET. The relation  $f(i_{ds})$  is approximated as

$$f(i_{ds}) = a + b \cdot i_{ds} + c \cdot i_{ds}^2 + d \cdot i_{ds}^3 + e \cdot i_{ds}^4. \quad (14)$$

It is convenient to represent  $f(i_{ds})$  as a polynomial expression to calculate (11). Fitting the relation of Fig. 1 to (14), each coefficient is shown in Table I. These value is empirically fitted to only one FET. From (11) and (14), the  $i_{ds0}$  value is obtained as 24.5 mA. It should be noted that this value is different from the condition that maximizes the  $IP_3$  of the unit gate width FET in Fig. 1. This result shows that we must simultaneously design the bias condition and the gate width to obtain the  $IP_{3max}$  of (13) at the target operating current.

In this paper, we use the measurement result to describe the function  $f(i_{ds})$ . Another way that describes  $f(i_{ds})$  is the use of the nonlinear FET model, such as Curtice cubic model [6], Statz model [7], and so on.

### IV. CALCULATION RESULT

In this section, the  $i_{ds0}$  value that is calculated in the previous section is discussed. It is worthwhile to compare this bias condition

TABLE I

COEFFICIENT VALUE OF THE FITTED EQUATION

| coefficient | fitted value                 |

|-------------|------------------------------|

| a           | -2.1 E2 mW                   |

| b           | 2.5 E1 mW / mA               |

| c           | 5.2 E-1 mW / mA <sup>2</sup> |

| d           | 4.2 E-3 mW / mA <sup>3</sup> |

| e           | 1.2 E-5 mW / mA <sup>4</sup> |

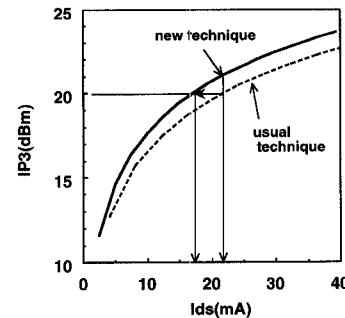

Fig. 2. Calculation results of the relation between  $I_{ds}$  and  $IP_3$ .

with usual one. Usually, the gate bias is set to the condition that maximizes  $IP_3$  for each gate width FET. In Fig. 1, this value is obtained as 40.1 mA. Therefore, it is different from the  $i_{ds0}$  value that is calculated in the previous section. Substituting these gate bias conditions to (13) and (14), the relation between  $IP_{3max}$  and  $I_{ds}$  as a parameter of the gate width is shown in Fig. 2. The solid line shows the relation with this new technique and the broken line shows that with usual one. In Fig. 2, the value of  $IP_3$  is increased by 1.2 dB to compare with the use of the usual technique at the  $I_{ds}$  of 21 mA. This figure also shows the  $I_{ds}$  value that is required to achieve the target  $IP_3$  value. For example, to obtain an  $IP_3$  of 20 dBm, the required  $I_{ds}$  is 21 mA for the usual technique. But it is 17 mA for this new one. This result shows that  $I_{ds}$  can be decreased by 20%. This new technique, for instance, contributes to the reduction of the consumption power for the machine of the cellular phone.

### V. CONCLUSION

A relation between the intermodulation distortion and the operating current as parameters of the gate bias condition and the gate width in microwave MESFET amplifiers has been presented. It shows that we must simultaneously design the gate bias condition and the gate width to achieve the maximum  $IP_3$  for the target  $I_{ds}$ . Using this new technique,  $I_{ds}$  can be reduced by 20% in comparison with the use of the usual one.

### ACKNOWLEDGMENT

The authors wish to thank Dr. D. Ueda, Dr. M. Kazumura and Dr. K. Itoh for useful discussions. They also thank Dr. G. Kano, who gives us the chance of proceeding this research.

### REFERENCES

- [1] R. A. Minasian, "Intermodulation Distortion Analysis of MESFET Amplifiers Using the Volterra Series Representation," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-28, pp. 1–8, Jan. 1980.

- [2] G. M. Lambrianou and C. S. Aitchison, "Optimization of Third-Order Intermodulation Product and Output Power from an X-Band MESFET

Amplifier Using Volterra Series Analysis," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-33, pp. 1395-1403, Dec. 1985.

[3] R. Gilmore, "Nonlinear Circuit Design Using the Modified Harmonic Balance Algorithm," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-34, pp. 1294-1307, Dec. 1986.

[4] A. M. Crosmun and S. A. Maas, "Minimization of Intermodulation Distortion in GaAs MESFET Small-Signal Amplifiers," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-34, pp. 1411-1416, Sept. 1989.

[5] S. A. Maas and D. Neilson, "Modeling MESFET's for Intermodulation Analysis of Mixers and Amplifiers," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-38, pp. 1964-1971, Dec. 1990.

[6] W. R. Curtice and M. Ettenberg, "A Nonlinear GaAs FET Model for use in the Design of Output Circuits for Power Amplifier," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-33, pp. 1383-1394, Dec. 1985.

[7] H. Statz, P. Newman, I. W. Smith, R. A. Pucel, and H. A. Haus, "GaAs FET Device and circuit Simulation in SPICE," *IEEE Trans. Electron Devices*, vol. ED-34, pp. 160-169, Feb. 1987.

## LRM Probe-Tip Calibrations using Nonideal Standards

Dylan F. Williams, and Roger B. Marks

**Abstract**—The line-reflect-match calibration is enhanced to accommodate imperfect match standards and lossy lines typical of monolithic microwave integrated circuits. We characterize the match and line standards using an additional line standard of moderate length. The new method provides a practical means of obtaining accurate, wideband calibrations with compact standard sets. Without the enhancement, calibration errors due to imperfections in typical standards can be severe.

### I. INTRODUCTION

This paper, which has been presented in conference [1], shows how line-reflect-match (LRM) calibrations of microwave probe stations can be extended to cases in which the match and line standards are imperfect.

Eul and Schiek [2] introduced LRM as an alternative to the thru-reflect-line (TRL) calibration [3]. They noted that the LRM calibration sets the reference impedance to the impedance of the match standard, which is generally unknown except at dc. This is further discussed in [4].

More recently, Barr and Pervere [5] studied the LRM calibration and noted that a characterization of the lossy line is also necessary in order to translate the reference plane. They did not suggest a means of performing this characterization, however. Davidson, *et al.* [6] applied the LRM technique with the intent of obtaining a probe-tip calibration, that is, a probe-station calibration with reference plane near the probe tips and reference impedance of 50  $\Omega$ . As a match standard, these authors used resistors trimmed to a dc resistance of 50  $\Omega$ . They attempted to determine the resistor reactance and concluded that it was small. They achieved the reference plane translation by using a very short low-loss line standard, estimating its parameters from lossless approximations. These implementations of the LRM calibration are therefore limited to ideal match standards and to short low-loss line standards.

Manuscript received February 7, 1994; revised May 27, 1994.

The authors are with the National Institute of Standards and Technology, Boulder, CO 80303 USA.

IEEE Log Number 9407309.

In [7], Davidson, *et al.* introduced a procedure which attempts to determine and account for the reactance of the planar resistors they used as match standards. They achieved this by introducing a lossless reflect into the calibration. This method is still limited to match standards with a frequency-independent resistance and with a reactance due only to a frequency-independent inductance, to short low-loss line standards, and to lossless reflects.

The multiline TRL calibration [8] does not suffer from these limitations. Because it is based on the TRL algorithm, it measures the ratios of traveling waves in the transmission lines [4]. The bandwidth and accuracy of the calibration are increased over conventional TRL by the use of multiple lines. The calibration also measures the propagation constant of the line standards so that the calibration reference impedance and the reference plane can be set accurately [9], [10]. The calibration is thus especially well suited to monolithic microwave integrated circuits (MMIC's), in which wide bandwidth is needed and small geometries result in very lossy lines with a complex frequency-dependent characteristic impedance.

The multiline TRL calibration suffers one important drawback, however. To obtain a wide measurement bandwidth, a set of lines, some quite long, is required; this uses expensive space on the wafer. When realized in MMIC form, LRM standards while far more compact than multiline TRL standards, are incompatible with conventional LRM assumptions. Typical imperfections include match standards with process-dependent dc resistance and frequency-dependent resistance and inductance [11], lossy line standards, and lossy reflects, are incompatible with the assumptions of conventional implementations of LRM.

In this paper we show how to modify the LRM calibration to account for the imperfect match and line standards typical of MMIC's. We first study coplanar waveguide (CPW) resistors and lines, evaluating separately their use as match and line standards in LRM probe-tip calibrations. We show that both the real and imaginary parts of the resistor impedance must be known if the LRM reference impedance, which is initially set to the impedance of the match, is to be reset to some standard value (e.g. 50  $\Omega$ ). We also show that the line loss and characteristic impedance must be considered when setting the reference plane position. Finally, we examine a TRL calibration with a single line moderately longer than the thru line and show that it is accurate enough in practice to characterize the match and line standards. This results in a practical means of obtaining accurate wideband calibrations with a compact standard set consisting of a thru line, a reflect, a match standard, and a second line standard of moderate length.

### II. REFERENCE IMPEDANCE

For these experiments we constructed a set of CPW calibration artifacts, typical of those found on MMIC's, on a gallium arsenide substrate. The artifacts consisted of a CPW thru line 550  $\mu\text{m}$  long, four longer lines of length 2.685 mm, 3.75 mm, 7.115 mm, and 20.245 mm, and two shorts offset 0.225 mm from the beginning of the line. We also fabricated a match standard by terminating a 275  $\mu\text{m}$  section of the CPW with a single 73  $\mu\text{m}$  by 73  $\mu\text{m}$  nickel-chromium thin-film resistor; the resistor geometry is described in [11]. These artifacts were fabricated with a 0.5  $\mu\text{m}$  evaporated gold film adhered to the 500  $\mu\text{m}$  gallium arsenide substrate with an approximately 50 nm titanium adhesion layer. The lines had a center conductor of width 73  $\mu\text{m}$  separated from two 250  $\mu\text{m}$  ground planes by 49  $\mu\text{m}$  gaps.